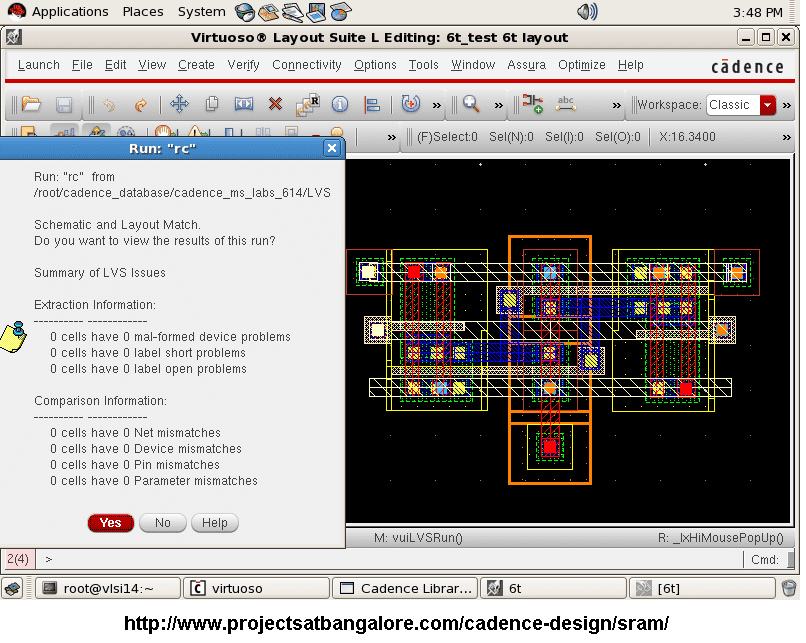

There are two key features to SRAM - Static random Access Memory, and these set it out against other types of memory that are available: The circuit for an individual SRAM memory cell comprises typically four transistors configured as two cross coupled inverters.Cadence Circuit of sram design-In this format the circuit has two stable states, and these equate to the logical "0" and "1" states. In addition to the four transistors in the basic memory cell, and additional two transistors are required to control the access to the memory cell during the read and write operations. This makes a total of six transistors, making what is termed a 6T memory cell. Sometimes further transistors are used to give either 8T or 10T memory cells. These additional transistors are used for functions such as implementing additional ports in a register file, etc for the SRAM memory. Although any three terminal switch device can be used in an SRAM, MOSFETs and in particular CMOS technology is normally used to ensure that very low levels of power consumption are achieved.sram design in cadence-With semiconductor memories extending to very large dimensions, each cell must achieve a very low levels of power consumption to ensure that the overall chip does not dissipate too much power. The operation of the SRAM memory cell is relatively straightforward. When the cell is selected, the value to be written is stored in the cross-coupled flip-flops. The cells are arranged in a matrix, with each cell individually addressable. Most SRAM memories select an entire row of cells at a time, and read out the contents of all the cells in the row along the column lines. While it is not necessary to have two bit lines, using the signal and its inverse, this is normal practice which improves the noise margins and improves the data integrity. The two bit lines are passed to two input ports on a comparator to enable the advantages of the differential data mode to be accessed, and the small voltage swings that are present can be more accurately detected. SRAM (Static Random Access Memory)

sram based fpga

SRAM memory cell operation

sram based FIFO